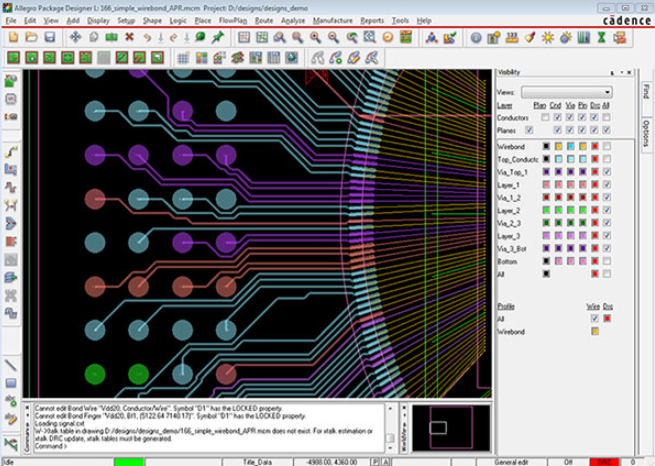

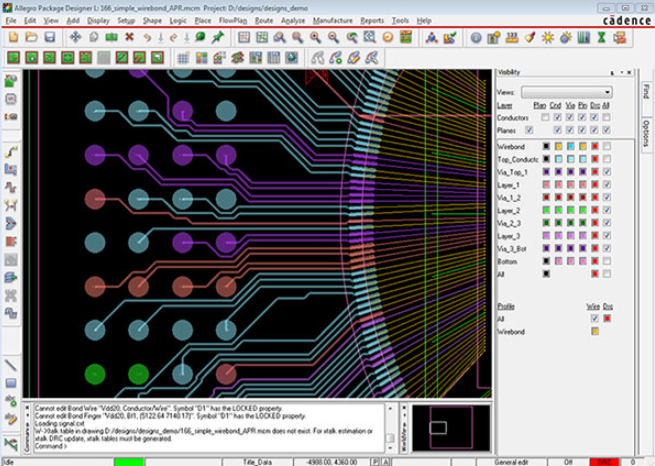

cadence版图绘制

软件: cadence

Cadence版图绘制完整流程与关键操作指南

一、前期准备:工艺库与项目环境

在开始版图绘制前,需完成以下基础配置:

选择工艺库:根据设计需求(如模拟/数字电路、工艺节点),选择合适的工艺库(如SMIC 18mmrf、TSMC 28nm等),工艺库包含版图层定义、设计规则(DRC)及寄生参数模型。

创建项目:通过Cadence Library Manager新建设计库,关联已选的工艺库和技术文件(Tech File),确保后续设计调用正确的层信息和规则。

原理图验证:完成原理图绘制后,确认所有器件(如MOS管、电阻、电容)的引脚(如VIN、VOUT、VDD、GND)已设置为顶层引脚(名称大写),并通过“Launch→Layout XL”将原理图器件导入版图环境。

二、版图绘制核心步骤

1. 器件导入与初始布局

导入原理图器件:在版图界面选择Connectivity→Generate→Selected From Source,勾选“Instances”选项,将原理图中的器件批量导入版图。导入后可按Shift+F显示器件内部结构(如MOS管的有源区、栅极),Ctrl+F返回宏观视角。

初始布局原则:优先考虑工艺约束(如NMOS需放置在P型衬底上,PMOS需放置在N阱中)、匹配需求(如差分对MOS管对称放置,保持沟道长度、宽度一致)及布线便利性(如电源、地靠近器件,减少走线长度)。布局时可使用m键移动器件,a键对齐(点击器件边缘实现边对齐,点击中心圆点实现中心对齐),Shift+G快速添加Guard Ring(保护环,用于隔离噪声)。

2. 关键图层绘制:有源区、栅极、阱

有源区(Active):代表MOS管的有源区(沟道区域),使用LSW窗口选择Active(dg)层(dg表示Drawing),通过Rectangle工具绘制矩形。例如,NMOS有源区尺寸需根据设计规则(如沟道长度L=0.18μm、宽度W=1.2μm)确定,绘制后需与栅极精确重叠。

栅极(Poly):MOS管的控制电极,使用Poly(dg)层绘制。通常用Path工具绘制细长矩形(线宽需符合设计规则,如0.06μm),确保栅极与有源区两端重叠(形成源/漏区)。

阱(Well):PMOS管需放置在N阱中,使用NWell层绘制。N阱需覆盖PMOS有源区,并预留足够空间(如与P型衬底间距≥6λ),避免穿通效应。

3. 连接与布线:金属层、过孔

金属层选择:电源(VDD)、地(GND)通常用Metal1层(水平布线),信号线用Metal1(水平)+Metal2(垂直)组合,减少寄生参数。

过孔添加:连接不同金属层的关键结构,使用Via工具(如M1_AA表示连接Metal1与Active层)。绘制时选择过孔类型,设置尺寸(如1×1μm),覆盖在金属层边缘,确保与金属层完全重叠。

布线技巧:使用P键启动布线,点击图层边缘开始走线,F3进入编辑模式调整线宽(如Metal1线宽≥0.6μm,满足电流承载能力)。信号线需避免锐角(用45°线替代),减少信号反射;电源、地线需加粗(如Metal1线宽≥1.2μm),降低电阻压降。

4. 匹配设计:差分对与阵列

差分对MOS管:对称放置(如左右对称),确保沟道长度、宽度一致,栅极连线长度相等,减少失调电压。

MOS管阵列:对于多指MOS管(如放大器输入级),使用Array工具批量生成,保持手指间距一致(如≥2λ),提高匹配精度。

三、验证与优化:DRC、LVS、PEX

1. 设计规则检查(DRC)

使用Cadence的DIVA或Assura工具运行DRC,导入工艺库提供的.rul文件(如scmos.rul),检查版图是否符合工艺制造要求(如线宽、间距、重叠量)。若出现错误(如红线标记),需修改对应图层(如调整过孔尺寸、扩大金属间距),直至全部通过。

2. 版图与原理图一致性检查(LVS)

通过Calibre或Assura运行LVS,导入原理图网表(.spice)和版图网表(.ext),检查器件数量、连接关系是否一致。若出现未连接节点(如MOS管源极未接VSS),需修改版图(如添加过孔、连线),确保与原理图匹配。

3. 寄生参数提取(PEX)

使用Calibre提取版图寄生参数(如电阻、电容、电感),生成.spef文件,用于后仿真。寄生参数会影响电路性能(如增益、带宽),需通过后仿真验证设计是否满足指标要求,若不满足,需调整版图(如缩短信号线长度、增加过孔数量)。

四、常用快捷键与技巧

移动与复制:m键移动器件,c键复制(按住Shift可选择复制属性,如层、尺寸),Shift+Z放大选中区域,Ctrl+Z撤销操作。

对齐与分组:a键进入对齐模式,点击器件边缘实现边对齐;Edit→Group将多个器件捆绑,便于整体移动或对齐。

过孔与布线:o键添加过孔,P键布线,Q键修改线宽,K键显示/隐藏尺子(用于测量距离)。

通过上面流程,可完成Cadence版图的基础绘制与验证。实际设计中需根据具体电路(如模拟放大器、数字逻辑门)调整细节(如匹配精度、寄生参数控制),并结合工艺库的设计规则优化版图性能。

一、前期准备:工艺库与项目环境

在开始版图绘制前,需完成以下基础配置:

选择工艺库:根据设计需求(如模拟/数字电路、工艺节点),选择合适的工艺库(如SMIC 18mmrf、TSMC 28nm等),工艺库包含版图层定义、设计规则(DRC)及寄生参数模型。

创建项目:通过Cadence Library Manager新建设计库,关联已选的工艺库和技术文件(Tech File),确保后续设计调用正确的层信息和规则。

原理图验证:完成原理图绘制后,确认所有器件(如MOS管、电阻、电容)的引脚(如VIN、VOUT、VDD、GND)已设置为顶层引脚(名称大写),并通过“Launch→Layout XL”将原理图器件导入版图环境。

二、版图绘制核心步骤

1. 器件导入与初始布局

导入原理图器件:在版图界面选择Connectivity→Generate→Selected From Source,勾选“Instances”选项,将原理图中的器件批量导入版图。导入后可按Shift+F显示器件内部结构(如MOS管的有源区、栅极),Ctrl+F返回宏观视角。

初始布局原则:优先考虑工艺约束(如NMOS需放置在P型衬底上,PMOS需放置在N阱中)、匹配需求(如差分对MOS管对称放置,保持沟道长度、宽度一致)及布线便利性(如电源、地靠近器件,减少走线长度)。布局时可使用m键移动器件,a键对齐(点击器件边缘实现边对齐,点击中心圆点实现中心对齐),Shift+G快速添加Guard Ring(保护环,用于隔离噪声)。

2. 关键图层绘制:有源区、栅极、阱

有源区(Active):代表MOS管的有源区(沟道区域),使用LSW窗口选择Active(dg)层(dg表示Drawing),通过Rectangle工具绘制矩形。例如,NMOS有源区尺寸需根据设计规则(如沟道长度L=0.18μm、宽度W=1.2μm)确定,绘制后需与栅极精确重叠。

栅极(Poly):MOS管的控制电极,使用Poly(dg)层绘制。通常用Path工具绘制细长矩形(线宽需符合设计规则,如0.06μm),确保栅极与有源区两端重叠(形成源/漏区)。

阱(Well):PMOS管需放置在N阱中,使用NWell层绘制。N阱需覆盖PMOS有源区,并预留足够空间(如与P型衬底间距≥6λ),避免穿通效应。

3. 连接与布线:金属层、过孔

金属层选择:电源(VDD)、地(GND)通常用Metal1层(水平布线),信号线用Metal1(水平)+Metal2(垂直)组合,减少寄生参数。

过孔添加:连接不同金属层的关键结构,使用Via工具(如M1_AA表示连接Metal1与Active层)。绘制时选择过孔类型,设置尺寸(如1×1μm),覆盖在金属层边缘,确保与金属层完全重叠。

布线技巧:使用P键启动布线,点击图层边缘开始走线,F3进入编辑模式调整线宽(如Metal1线宽≥0.6μm,满足电流承载能力)。信号线需避免锐角(用45°线替代),减少信号反射;电源、地线需加粗(如Metal1线宽≥1.2μm),降低电阻压降。

4. 匹配设计:差分对与阵列

差分对MOS管:对称放置(如左右对称),确保沟道长度、宽度一致,栅极连线长度相等,减少失调电压。

MOS管阵列:对于多指MOS管(如放大器输入级),使用Array工具批量生成,保持手指间距一致(如≥2λ),提高匹配精度。

三、验证与优化:DRC、LVS、PEX

1. 设计规则检查(DRC)

使用Cadence的DIVA或Assura工具运行DRC,导入工艺库提供的.rul文件(如scmos.rul),检查版图是否符合工艺制造要求(如线宽、间距、重叠量)。若出现错误(如红线标记),需修改对应图层(如调整过孔尺寸、扩大金属间距),直至全部通过。

2. 版图与原理图一致性检查(LVS)

通过Calibre或Assura运行LVS,导入原理图网表(.spice)和版图网表(.ext),检查器件数量、连接关系是否一致。若出现未连接节点(如MOS管源极未接VSS),需修改版图(如添加过孔、连线),确保与原理图匹配。

3. 寄生参数提取(PEX)

使用Calibre提取版图寄生参数(如电阻、电容、电感),生成.spef文件,用于后仿真。寄生参数会影响电路性能(如增益、带宽),需通过后仿真验证设计是否满足指标要求,若不满足,需调整版图(如缩短信号线长度、增加过孔数量)。

四、常用快捷键与技巧

移动与复制:m键移动器件,c键复制(按住Shift可选择复制属性,如层、尺寸),Shift+Z放大选中区域,Ctrl+Z撤销操作。

对齐与分组:a键进入对齐模式,点击器件边缘实现边对齐;Edit→Group将多个器件捆绑,便于整体移动或对齐。

过孔与布线:o键添加过孔,P键布线,Q键修改线宽,K键显示/隐藏尺子(用于测量距离)。

通过上面流程,可完成Cadence版图的基础绘制与验证。实际设计中需根据具体电路(如模拟放大器、数字逻辑门)调整细节(如匹配精度、寄生参数控制),并结合工艺库的设计规则优化版图性能。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...