cadence把电路图变成版图

软件: cadence

Cadence从原理图到版图的完整流程

将电路原理图转换为可制造的版图(Layout)是集成电路设计的关键环节,Cadence提供了多种工具(如OrCAD Capture CIS、Virtuoso、Allegro)实现这一流程,核心步骤可分为前期准备、器件导入、布局布线、验证优化四大类,以下是详细操作说明:

一、前期准备:确保原理图与库文件正确性

在启动版图设计前,需完成两项基础工作:

1. 原理图验证:完成电路原理图绘制(如使用OrCAD Capture CIS),并为所有元器件添加引脚(Pin)(注意引脚名称需大写,如VDD、GND);运行DRC(设计规则检查),确保原理图无电气冲突(如未连接引脚、短路);生成Netlist(网表),这是原理图与版图的“桥梁”,包含所有元器件及连接信息。

2. 库文件准备:确认工艺库(如SMIC 18mm RF、TSMC 16nm)已正确安装,库中包含器件版图(如MOS管、电阻)、焊盘(Pad)、封装(Package)等信息,确保原理图中的元器件与库中模型一致。

二、器件导入:将原理图元件映射到版图

1. 传统方法:手动导入器件

- 打开Cadence版图工具(如Virtuoso Layout Editor),新建版图文件(File → New → Layout);

- 通过“File → Import → Capture Schematic”导入原理图,或使用“Create → Cellview → From Cellview”(选择原理图文件)生成版图单元;

- 导入后,通过“Shift+F”显示器件细节,调整器件位置(使用M键移动),确保布局符合初步设计要求。

2. 进阶方法:SDL(原理图驱动布局)

- 适用于模拟/射频电路(如运放、ADC),打开原理图后运行“SDL → Generate Hierarchy”;

- 在弹出界面中勾选Keep Topology Schematic To Layout(保持原理图与版图拓扑一致),设置Scale(原理图到版图的尺寸比例,如30倍),点击“OK”自动生成版图框架;

- 此方法可保留原理图的连接关系,减少手动布局的工作量。

三、布局与布线:构建物理连接

1. 器件布局

- 根据电路功能(如信号流向、电源分布)摆放器件,优先放置核心元件(如运放的输入级、输出级);

- 遵循设计规则:如MOS管的沟道长度方向(通常沿晶圆切割线)、电容的对称布局(减少寄生参数)、电源器件的分散放置(降低IR压降);

- 使用“Mirror Y”(Y轴镜像)实现差分对的对称布局,“Fold Number”(折叠数)调整MOS管的排列模式(如ABBA→ABAB,优化匹配性)。

2. 过孔与布线

- 过孔添加:使用“O”键添加过孔(如M1_AA连接金属层1与有源区),选择合适的过孔尺寸(如直径0.2μm,间距0.4μm);

- 金属布线:使用“P”键绘制金属线(如M1层蓝色线条),连接相同网络名称的引脚(如VDD、GND);

- 寄生参数提取:布线完成后,运行“PEX(寄生参数提取)”,生成寄生电阻、电容模型(如Rwire、Cjunction),用于后续后仿真。

3. 引脚标注

- 在版图上添加端口标签(如VDD、GND),对应原理图中的引脚名称,确保电气连接正确;

- 使用“Label”工具标注关键信号(如输入/输出端),提高版图可读性。

四、验证与优化:确保版图正确性

1. DRC(设计规则检查)

- 运行版图工具中的“DRC”命令,加载工艺库提供的规则文件(如SMIC 18mm RF的DRC规则);

- 检查常见错误:过孔与金属层间距不足、器件重叠、布线超出芯片边界;

- 修复所有DRC错误(通常需多次迭代),确保版图符合制造要求。

2. LVS(版图与原理图一致性检查)

- 运行“LVS”命令,加载工艺库中的“LVS rules_file”(如电源/地检查规则);

- 对比版图与原理图的器件数量、连接关系,若结果显示“Smiley Face”(笑脸),则表示一致;

- 若存在差异(如未连接的引脚),需手动检查并修正。

3. 后仿真

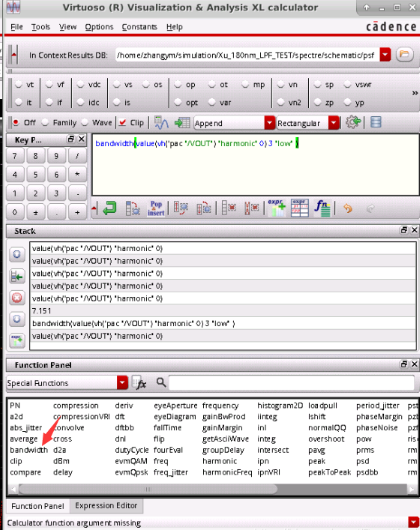

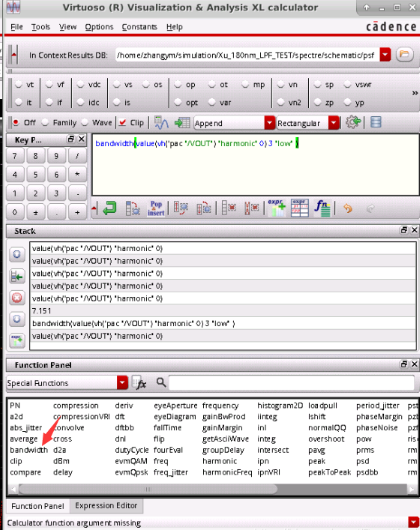

- 提取寄生参数后,使用Cadence Spectre或AMS工具进行后仿真;

- 验证电路在实际版图中的性能(如增益、带宽、功耗),若不符合设计要求,需返回布局布线阶段优化(如调整器件位置、优化布线长度)。

五、导出版图:生成制造文件

- 完成所有验证与优化后,运行“Export → Layout”命令,导出版图文件(如GDSII格式);

- GDSII文件包含版图的所有几何信息(如器件形状、布线路径),是晶圆厂制造芯片的依据;

- 导出前需确认文件版本、层定义(如金属层、有源区)与工艺库一致。

以上流程涵盖了Cadence从原理图到版图的核心步骤,实际设计中需根据电路类型(数字/模拟、射频/低功耗)调整细节(如模拟电路更注重器件匹配,数字电路更注重布线延迟)。通过严格遵循设计规则与验证流程,可确保版图的正确性与可靠性,为后续芯片制造奠定基础。

将电路原理图转换为可制造的版图(Layout)是集成电路设计的关键环节,Cadence提供了多种工具(如OrCAD Capture CIS、Virtuoso、Allegro)实现这一流程,核心步骤可分为前期准备、器件导入、布局布线、验证优化四大类,以下是详细操作说明:

一、前期准备:确保原理图与库文件正确性

在启动版图设计前,需完成两项基础工作:

1. 原理图验证:完成电路原理图绘制(如使用OrCAD Capture CIS),并为所有元器件添加引脚(Pin)(注意引脚名称需大写,如VDD、GND);运行DRC(设计规则检查),确保原理图无电气冲突(如未连接引脚、短路);生成Netlist(网表),这是原理图与版图的“桥梁”,包含所有元器件及连接信息。

2. 库文件准备:确认工艺库(如SMIC 18mm RF、TSMC 16nm)已正确安装,库中包含器件版图(如MOS管、电阻)、焊盘(Pad)、封装(Package)等信息,确保原理图中的元器件与库中模型一致。

二、器件导入:将原理图元件映射到版图

1. 传统方法:手动导入器件

- 打开Cadence版图工具(如Virtuoso Layout Editor),新建版图文件(File → New → Layout);

- 通过“File → Import → Capture Schematic”导入原理图,或使用“Create → Cellview → From Cellview”(选择原理图文件)生成版图单元;

- 导入后,通过“Shift+F”显示器件细节,调整器件位置(使用M键移动),确保布局符合初步设计要求。

2. 进阶方法:SDL(原理图驱动布局)

- 适用于模拟/射频电路(如运放、ADC),打开原理图后运行“SDL → Generate Hierarchy”;

- 在弹出界面中勾选Keep Topology Schematic To Layout(保持原理图与版图拓扑一致),设置Scale(原理图到版图的尺寸比例,如30倍),点击“OK”自动生成版图框架;

- 此方法可保留原理图的连接关系,减少手动布局的工作量。

三、布局与布线:构建物理连接

1. 器件布局

- 根据电路功能(如信号流向、电源分布)摆放器件,优先放置核心元件(如运放的输入级、输出级);

- 遵循设计规则:如MOS管的沟道长度方向(通常沿晶圆切割线)、电容的对称布局(减少寄生参数)、电源器件的分散放置(降低IR压降);

- 使用“Mirror Y”(Y轴镜像)实现差分对的对称布局,“Fold Number”(折叠数)调整MOS管的排列模式(如ABBA→ABAB,优化匹配性)。

2. 过孔与布线

- 过孔添加:使用“O”键添加过孔(如M1_AA连接金属层1与有源区),选择合适的过孔尺寸(如直径0.2μm,间距0.4μm);

- 金属布线:使用“P”键绘制金属线(如M1层蓝色线条),连接相同网络名称的引脚(如VDD、GND);

- 寄生参数提取:布线完成后,运行“PEX(寄生参数提取)”,生成寄生电阻、电容模型(如Rwire、Cjunction),用于后续后仿真。

3. 引脚标注

- 在版图上添加端口标签(如VDD、GND),对应原理图中的引脚名称,确保电气连接正确;

- 使用“Label”工具标注关键信号(如输入/输出端),提高版图可读性。

四、验证与优化:确保版图正确性

1. DRC(设计规则检查)

- 运行版图工具中的“DRC”命令,加载工艺库提供的规则文件(如SMIC 18mm RF的DRC规则);

- 检查常见错误:过孔与金属层间距不足、器件重叠、布线超出芯片边界;

- 修复所有DRC错误(通常需多次迭代),确保版图符合制造要求。

2. LVS(版图与原理图一致性检查)

- 运行“LVS”命令,加载工艺库中的“LVS rules_file”(如电源/地检查规则);

- 对比版图与原理图的器件数量、连接关系,若结果显示“Smiley Face”(笑脸),则表示一致;

- 若存在差异(如未连接的引脚),需手动检查并修正。

3. 后仿真

- 提取寄生参数后,使用Cadence Spectre或AMS工具进行后仿真;

- 验证电路在实际版图中的性能(如增益、带宽、功耗),若不符合设计要求,需返回布局布线阶段优化(如调整器件位置、优化布线长度)。

五、导出版图:生成制造文件

- 完成所有验证与优化后,运行“Export → Layout”命令,导出版图文件(如GDSII格式);

- GDSII文件包含版图的所有几何信息(如器件形状、布线路径),是晶圆厂制造芯片的依据;

- 导出前需确认文件版本、层定义(如金属层、有源区)与工艺库一致。

以上流程涵盖了Cadence从原理图到版图的核心步骤,实际设计中需根据电路类型(数字/模拟、射频/低功耗)调整细节(如模拟电路更注重器件匹配,数字电路更注重布线延迟)。通过严格遵循设计规则与验证流程,可确保版图的正确性与可靠性,为后续芯片制造奠定基础。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...