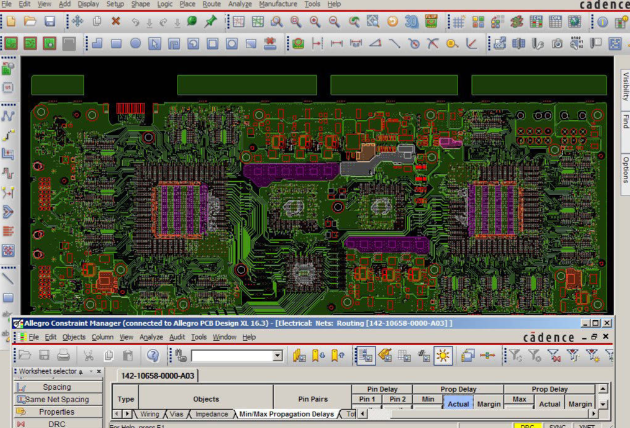

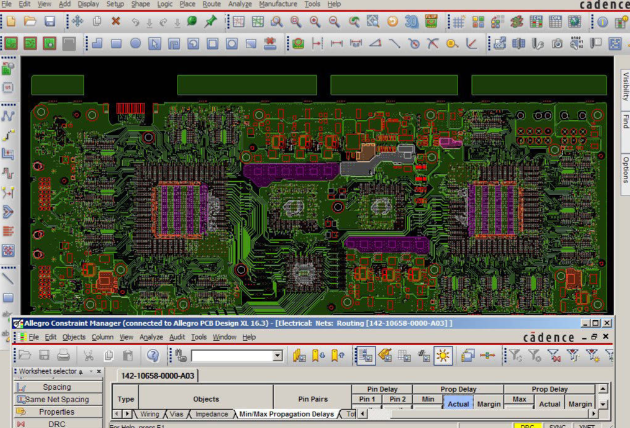

cadence版图设计教程

软件: cadence

以下是Cadence Virtuoso版图设计的主要步骤,综合了多个教程和资源中的核心流程:

1. 前期准备

完成原理图设计:确保电路原理图(Schematic)已通过前仿真(Pre-Layout Simulation),包括DC、AC、瞬态等基本仿真以及工艺角(Corner)和蒙特卡洛(Monte Carlo)等鲁棒性验证。所有器件参数需为确定值,且模型必须来自目标工艺库。

获取设计规则:从晶圆厂提供的设计规则手册(Design Rule Manual)中明确工艺参数(如最小线宽、间距等)。

2. 版图生成与布局

创建版图单元:在Virtuoso Layout Editor中新建版图视图(Cellview),关联工艺库。

导入器件:通过Generate All from Source或Place as in schematic将原理图器件自动导入版图,或使用Place > Analog > Automatic Placement优化布局。

添加Dummy器件:在关键区域(如匹配晶体管周围)添加Dummy器件以提高工艺一致性。

Guard Ring设计:手动或通过Modgen > Guard Ring添加保护环(Guard Ring),隔离噪声并改善衬底连接。

3. 布线与连接

金属连线:遵循“奇竖偶横”原则(奇数层金属走竖线,偶数层走横线),优先连接器件内部网络。使用快捷键(如p绘制路径,o添加过孔)提高效率。

层管理:依次绘制NWELL/PWELL、Active Area(AA)、POLY栅极、接触孔(CONT)、金属层(M1-Mx)等,确保符合工艺层定义。

4. 验证与修正

DRC检查:运行设计规则检查(DRC),修正间距、宽度等几何违规问题。工具如Assura或Calibre会标注错误位置。

LVS验证:确保版图与原理图一致(LVS),修复短路、开路或器件参数不匹配等问题。

寄生参数提取(PEX):提取版图中的寄生电阻/电容,用于后仿真(Post-Layout Simulation)。

5. 后仿真与流片

后仿真:将PEX生成的寄生参数网表导入仿真环境(如Spectre),验证电路性能是否满足要求。

生成流片文件:通过验证后,导出GDSII等格式文件提交给晶圆厂,并根据反馈调整设计。

实用技巧与资源

快捷键设置:通过.cdsinit文件自定义快捷键(如空格旋转、右键替代Esc),提升操作效率。

学习资源:推荐Cadence官方文档(如《Virtuoso Layout Suite XL User Guide》)和社区教程(如知乎专栏或CSDN博客)。

以上步骤涵盖了从设计到验证的全流程,具体操作可能因工艺或项目需求略有差异。建议结合工艺库文档和实际案例(如反相器或D触发器版图)练习。

1. 前期准备

完成原理图设计:确保电路原理图(Schematic)已通过前仿真(Pre-Layout Simulation),包括DC、AC、瞬态等基本仿真以及工艺角(Corner)和蒙特卡洛(Monte Carlo)等鲁棒性验证。所有器件参数需为确定值,且模型必须来自目标工艺库。

获取设计规则:从晶圆厂提供的设计规则手册(Design Rule Manual)中明确工艺参数(如最小线宽、间距等)。

2. 版图生成与布局

创建版图单元:在Virtuoso Layout Editor中新建版图视图(Cellview),关联工艺库。

导入器件:通过Generate All from Source或Place as in schematic将原理图器件自动导入版图,或使用Place > Analog > Automatic Placement优化布局。

添加Dummy器件:在关键区域(如匹配晶体管周围)添加Dummy器件以提高工艺一致性。

Guard Ring设计:手动或通过Modgen > Guard Ring添加保护环(Guard Ring),隔离噪声并改善衬底连接。

3. 布线与连接

金属连线:遵循“奇竖偶横”原则(奇数层金属走竖线,偶数层走横线),优先连接器件内部网络。使用快捷键(如p绘制路径,o添加过孔)提高效率。

层管理:依次绘制NWELL/PWELL、Active Area(AA)、POLY栅极、接触孔(CONT)、金属层(M1-Mx)等,确保符合工艺层定义。

4. 验证与修正

DRC检查:运行设计规则检查(DRC),修正间距、宽度等几何违规问题。工具如Assura或Calibre会标注错误位置。

LVS验证:确保版图与原理图一致(LVS),修复短路、开路或器件参数不匹配等问题。

寄生参数提取(PEX):提取版图中的寄生电阻/电容,用于后仿真(Post-Layout Simulation)。

5. 后仿真与流片

后仿真:将PEX生成的寄生参数网表导入仿真环境(如Spectre),验证电路性能是否满足要求。

生成流片文件:通过验证后,导出GDSII等格式文件提交给晶圆厂,并根据反馈调整设计。

实用技巧与资源

快捷键设置:通过.cdsinit文件自定义快捷键(如空格旋转、右键替代Esc),提升操作效率。

学习资源:推荐Cadence官方文档(如《Virtuoso Layout Suite XL User Guide》)和社区教程(如知乎专栏或CSDN博客)。

以上步骤涵盖了从设计到验证的全流程,具体操作可能因工艺或项目需求略有差异。建议结合工艺库文档和实际案例(如反相器或D触发器版图)练习。

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...