分享:我用Cadence Xcelium 19.09成功运行FreeARM7内核的经验

凭借Cadence Xcelium 19.09成功仿真FreeARM7内核:一个实践者的经验分享

引言

本文探索了一个使用Cadence Xcelium 19.09集成环境,成功加载FreeARM7内核实例的完整工作流程。通过提供测试环境配置、关键文件概述和详细实验步骤,旨在演示如何借助经典ECAP(Electronic ComputerAided Prototyping)工具实现ARM微控制器核心的硬件仿真。

所需环境和配置

硬件仿真平台:Cadence Xcelium 19.09,最新稳定版本的硬件描述语言(HDL)仿真工具,支持广泛的数字设计技术。

测试软件:FreeARM7内核,用于验证和测试的开源ARM处理器实例;uCLinux操作系统镜像,为FreeARM7提供软件环境支持。

测试文件:

`arm6.v`:FreeARM7 CPU内核的Hardware Description Language (HDL)描述文件,包含详细的高性能微处理器硬件逻辑。

`boot0.bin`:固化在非易失性存储介质上的内核启动镜像。

`FreeARM7_intro.pdf`:内核的简要介绍文档,帮助理解其基本结构和功能。

`tb_sp.v`:TestBench(测试模板)设计,用于定义与FreeARM7集成的激励信号、响应预期和仿真验证流程。

`uclinux0.bin`:uCLinux 操作系统镜像,用于加载到RAM中,使得FreeARM7能够在仿真环境中执行应用软件。

工作目录内环境变量与配置:确保Cadence工具链、合法的许可证文件路径以及任何驱动程序或库适配件得以正确设置。执行特定脚本(如`cshrc`和`bashrc`)来预先配置环境。

实验步骤

1. 环境准备:将所有必要的HDL文件和_binary镜像置于Cadence项目工作目录内,确保所有依赖项可被本地系统检测和调用。

2. 加载HDL文件:

使用命令 `xmverilog tb_sp.v` (或对早期版本兼容命令 `ncverilog tb_sp.v`)启动仿真图界面,加载并初始化TestBench (`tb_sp.v`),设置仿真控制流程以配置仿真参数,例如预加载ROM镜像和uCLinux二进制文件到相应的内存地址空间。

3. 启动系统测试编译:根据所给步骤,构建和优化FreeARM7内核,确保已适配特定的外围硬件组件,比如标准系统内存管理单元(Memory Management Unit, MMU)、中断控制器和USB控制器等。

4. 系统初始化与引导:执行内核启动过程,从非易失性存储设备上加载ROM镜像;初始化内核硬件组件,加载uCLinux操作系统镜像到RAM。

5. 监视系统行为:通过`$fdisplay`命令输出日志文件`log.txt`,记录内核在仿真环境中的执行细节,包括指令执行、寄存器内容、状态和性能数据等。

6. 登录与操作:系统加载uCLinux后,“登录”提示符出现,预示仿真进入最终状态。

7. 仿真结束:观看或记录日志文件中包含的序列,逐步分析输出信息,评估FreeARM7内核在模拟环境下的性能、稳定性以及与预期的差异。

成功标志与问题关联

实验的关键成功标志即是在模拟环境下,FreeARM7内核的逻辑正确执行,以及uCLinux操作系统能够稳定响应各种内核活动和外部输入。

实验中可能遇到的问题包括但不限于:

HDL描述文件中的编码错误或逻辑不一致。

仿真工具与测试Benchmark配置的兼容性问题。

系统级初始化过程的不正确处理。

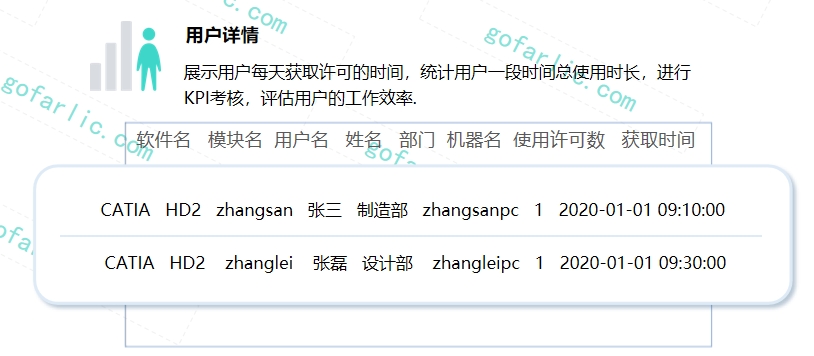

武汉格发信息技术有限公司,格发许可优化管理系统可以帮你评估贵公司软件许可的真实需求,再低成本合规性管理软件许可,帮助贵司提高软件投资回报率,为软件采购、使用提供科学决策依据。支持的软件有: CAD,CAE,PDM,PLM,Catia,Ugnx, AutoCAD, Pro/E, Solidworks ,Hyperworks, Protel,CAXA,OpenWorks LandMark,MATLAB,Enovia,Winchill,TeamCenter,MathCAD,Ansys, Abaqus,ls-dyna, Fluent, MSC,Bentley,License,UG,ug,catia,Dassault Systèmes,AutoDesk,Altair,autocad,PTC,SolidWorks,Ansys,Siemens PLM Software,Paradigm,Mathworks,Borland,AVEVA,ESRI,hP,Solibri,Progman,Leica,Cadence,IBM,SIMULIA,Citrix,Sybase,Schlumberger,MSC Products...